Kurz und knackig:

netpp – das Protokoll für Internet Of Things

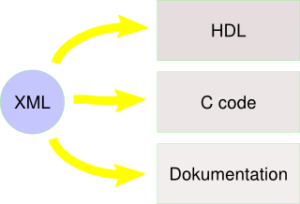

Gerätebeschreibungssprache mit grafischer Erstellung

Erzeuge Source (HDL, Software), Dokumentation

Verwalte hunderte von Geräten

Sprich mit intelligenten Geräten: benannte Eigenschaften anstatt Register!

‘IoF’: Internet of FPGAs

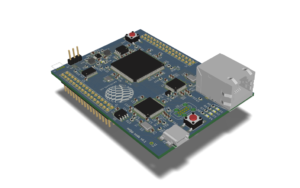

Hochzuverlässige Test&Messplattform, netpp-fähig und programmierbar. Links (englisch):

[ News ] [ Buy eval kit ]

Highlights:

Zyklengenau simulierbares Betriebssystem für zuverlässige Fernsteuerung per Netzwerk im on-chip RAM

Echtzeitfähige Peripherie, anpassbar an Kundenwünsche

In-System-Upgrade: Firmware-Updates per Netzwerk

Flexible Analogeingänge mit unterschiedlichen Bestückungsvarianten (msp430)

Dokumentation (englisch): [sdm_download id=”1422″ fancy=”0″]

CAP Anwendungsprozessor für FPGAs

Auf Basis der gut etablierten ZPU-Architektur wurde ein 32-Bit Prozessordesign an der Embedded World 2016 vorgestellt (mehr dazu hier ), welches sich gut für robuste Netzwerklösungen (“IoT”) oder anwendungsspezifische Szenarien wie Echtzeit-PWM-Steuerungen eignet.

Features:

freier Gnu Compiler-Support (GCC)

JTAG Hardware-Debugger (GDB single step, Sourcecode debugging)

Höchst kompakter Programmcode

Minimaler FPGA-Resourcenbedarf

Mikrocode-Support für DSP-Erweiterungen (“FLiX”)

Robustes IRQ-Verhalten, Erweiterungen für Failsafe-Szenarien (Watchdog, Checkpoints für korrekten Programmablauf)

Der CAP (Custom Application Prozessor) wird typischerweise als System-on-Chip mit fertiger Peripherie als FPGA-Bit-Image geliefert und kann in gängige FPGAs (s.u.) geladen werden. Je nach Anwendung und Kostenfaktor existieren verschiedene Standard-Konfigurationen:

agathe, anselm: Minimal-CPU mit PWM, UART, SPI

agneta: agathe-Derivat mit spezieller Mach XO2/3 EFB-Unterstützung

bertram: CAP mit Echtzeit-PWM und Unterstützung für grössere Programme im Flash

dagobert: Netzwerk-SoC mit Ethernet Controller (100M)

‘e’-Reihe: High-Speed DMA mit DualCore-Option

>> Zur Übersicht der SoC-Referenzdesigns

Vorteile

Beweisbare, voll simulierbare Prozessorfunktion (Simulationsmodelle verfügbar)

Schnelle Fehlersuche vom Programmcode bis zum Pin

Unabhängigkeit vom FPGA-Hersteller, Langzeitsupport

Anti-Kloning: Schützen Sie Ihr Know-How hinter kundenspezifischen Anpassungen und machen Sie Hardware-Hackern die Sache nicht zu einfach.

Unterstützte FPGA-Architekturen

Xilinx Spartan3, Spartan6, Kintex7

Lattice Semiconductor MachXO2, MachXO3, (ECP2), ECP3, ECP5

Portierung auf andere FPGAs ist im Rahmen eines Entwicklungspakets möglich

All SoC designs include the following peripherals by default:

Base: GPIO(2), SPI(1), TIMER(3), PWM(3), UART(1)

If multiple instances are possible, the maximum number of units configured for this SoC are listed in brackets.

SoC ID

CPU/Arch

SCACHE

IRQ

Peripherals

DMA

Reference platform

License

Applications

agathe Zealot/ZPU

n

1

PWM(8)

0

(1)

OS

Configuration µP

agneta

ZPUng v1

y

4

EFB MACHXO hard IPcore

0

(1)

C

Multi I/O PWM control

bertram ZPUng v1

y

4

PWMPLUS

0

(2)

C

Multi LED strip controller

dombert ZPUng v1.1

n

4

CPK, JPEG, MAC, DMAA

2

(3), (4), (5)

CS

MJPEG encoding/streaming SoC

dagobert ZPUng v1.1

y

6

MAC, PWM(3), DMAA

2

netpp node C

netpp/UDP SoC (Analog I/O)

emil ZPUng v2

RISC-V 32ui

y

6

MAC, DMAH, GDP, FLiX

4

(custom)

CS

High speed signal/data processing SoC, dual core capable

License codes:

OS: OpenSource, C: Source available under Custom agreement, CS: Closed Source, N/A: under development

Third party reference platforms

Mach XO2/XO3 breakout board [Link ]

Papilio Spartan3 250k [Link ]

Lattice HDR60 camera eval platform [Link ]

Lattice Versa ECP5G eval board [Link ]

Lattice EVDK (VIP) video processing eval board [Link ]

Trenz TE0600 based custom eval board [Link ]

Development kit

Peripheral IP Cores:

SCACHE: Virtual ROM (SPI cache). Enhances program memory up to several MB of ROM code for program overlay or data storage

DMA/DMAA : Simple DMA/Autobuffer DMA engine for high speed transfers with little CPU interference

LCDIO: Custom LCD driver engine

SPI: 32 bit word capable SPI I/O, DMA capable on d* SoCs.

TWI: proprietary i2c peripheral (with clock stretching)

PWMPLUS: Improved PWM for realtime pulse width control

FX2FIFO: Cypress FX2 FIFO interface for fast isochronous data transfer

GDP: Generic data port (Video or any other framed data)

MAC: Ethernet MAC interface for RGMII or GMII capable Phy Circuits

CPK: Proprietary image processing pipeline ‘COTTONPICKEN’

SPORT: Fast serial port for audio codec I/O, DMA capable

JPEG: JPEG hardware encoder

FLiX: proprietary microcode engine for DSP applications (ZPUng v2 only)

Continue reading SoC Overview