Martin Strubel section5.ch

# Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

02/2013

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 三臣 - のへぐ

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○ ○○○

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

1 Debugging a complex FPGA design (in theory)

- A SoC (System on Chip) example

- MAIS: A portable MIPS soft core by René Doss

- The Test Access Port (TAP): A generic debug interface

Ø Virtualizing the hardware

- 'Model in the loop' techniques

- Making real software speak to virtual hardware

#### 8 Demos

- Debugging the virtual chip

- Debugging the real hardware

Figure: Somewhat unreadable schematic

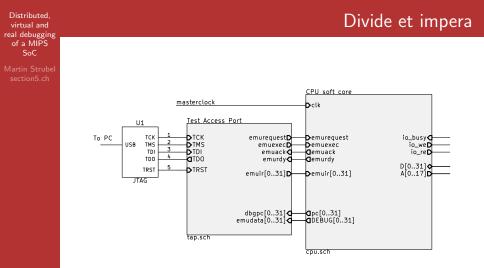

Figure: Simplified SoC schematic with Debug port

▲ロト ▲周ト ▲ヨト ▲ヨト 三日 - のくぐ

Existing solutions

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○ ○○○

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch Proprietary solutions from various FPGA vendors:

| Signal inspection tool | Soft CPU core | Vendor  |

|------------------------|---------------|---------|

| ChipScope              | microblaze    | Xilinx  |

| Reveal                 | mico32        | Lattice |

| SignalTap              | NiosII        | Altera  |

#### Table: Tool examples

- Virtualization capabilities depend on second party simulation tools (\$\$\$-\$\$\$\$\$)

- Debug port itself can sometimes not be simulated

Existing solutions

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch Proprietary solutions from various FPGA vendors:

| Signal inspection tool | Soft CPU core | Vendor  |

|------------------------|---------------|---------|

| ChipScope              | microblaze    | Xilinx  |

| Reveal                 | mico32        | Lattice |

| SignalTap              | NiosII        | Altera  |

#### Table: Tool examples

- Virtualization capabilities depend on second party simulation tools (\$\$\$-\$\$\$\$\$)

- Debug port itself can sometimes not be simulated

- No easy DIY virtualization of the hardware due to proprietary and closed libraries.

Martin Strube section5.ch

Introducing a soft cpu core **may** speed up prototyping/debugging.

(exercised previously with ZPU soft core)

#### Why MIPS?

- Well-established architecture with many derivatives (Loongson SoC, Router chipsets)

- Fast, easy to implement, resource saving

- Actively maintained tool chain and emulators

# The MIPS-compatible MAIS CPU

▲ロ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ● ○ ○ ○

Martin Strube section5.ch The MIPS-compatible MAIS CPU

▲ロ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ● ○ ○ ○

Introducing a soft cpu core **may** speed up prototyping/debugging.

(exercised previously with ZPU soft core)

#### Why MIPS?

- Well-established architecture with many derivatives (Loongson SoC, Router chipsets)

- Fast, easy to implement, resource saving

- Actively maintained tool chain and emulators

- MAIS design by René Doß:

- Well-portable MIPS 32 bit implementation

- Access to VHDL sources

# In Circuit Emulation (ICE)

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○ ○○○

SoC Martin Strube section5.ch

Distributed.

virtual and real debugging of a MIPS

In emulation mode, the CPU...

- takes opcodes from the EMUIR register

- executes them when it gets an emuexec pulse

- exchanges data with the debugger via the EMUDATA register

# In Circuit Emulation (ICE)

In emulation mode, the CPU...

Distributed.

virtual and real debugging of a MIPS SoC

- takes opcodes from the EMUIR register

- executes them when it gets an emuexec pulse

- exchanges data with the debugger via the EMUDATA register

Full remote control of the CPU via a test access port (TAP)!

#### Debugger components

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

> The developer's front end: The GNU debugger (gdb)

Figure: GDB

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○ ○○○

Debugger connects to back end via a TCP remote debugging protocol. Means: Distributed across networks!

### Debugger components

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

- The developer's front end: The GNU debugger (gdb)

- 2 The back ends:

- uniproxy: a JTAG debug server

- emu: a MIPS CPU emulator

| Ele Ban Yew Control Preferences Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 🐐 19 19 19 19 19 19 18 18 18 18 18 18 18 18 18 18 18 18 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 🛔 +2 🕮 Find: 🔤 🚽                                                                                                                                                                                            |

| main.c 💌 main 💌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SOURCE V                                                                                                                                                                                                    |

| 00 MARC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _BWIER;                                                                                                                                                                                                     |

| 121 Hendlif<br>Program not running. Click on run icon to start.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (Fac052) 114                                                                                                                                                                                                |

| PAN EST. Yoo Winner<br>Internet and the set of the set of the<br>temperature of the set of the set of the<br>temperature of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the<br>set of the set of the set of the set of the set of the<br>set of the set of the set of the set of the set of the<br>set of the set of the set of the set of the set of the<br>set of the set of the set of the set of the set of the<br>set of the set of the set of the set of the set of the<br>set of the set of the<br>set of the set of the | pt //greary main A<br>appright (0: 2009 doublety doarwat Stee,<br>2012 and<br>ANTER (12: 2012 by www.sattlands.ch<br>/mater.cptc: 00<br>/mater.cptc: 00<br>/mater.cptc: 00<br>jstg.com/fig in not supported |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                           |

Figure: GDB and uniproxy

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○ ○○○

Debugger connects to back end via a TCP remote debugging protocol. Means: Distributed across networks!

#### Debugger components

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

- The developer's front end: The GNU debugger (gdb)

- 2 The back ends:

- uniproxy: a JTAG debug server

- emu: a MIPS CPU emulator

- ITAG debugger hardware: USB JTAG adapter

#### Figure: ICEbear JTAG adapter

Debugger connects to back end via a TCP remote debugging protocol. Means: Distributed across networks!

▲□▶ ▲圖▶ ▲臣▶ ▲臣▶ 二臣 - わへぐ

Distributed, virtual and real debugging of a MIPS SoC

- qemu: software-emulated MIPS CPU a functional model

- Write C code to functionally emulate attached hardware

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○ ○○○

Distributed, virtual and real debugging of a MIPS SoC

- qemu: software-emulated MIPS CPU a functional model

- Write C code to functionally emulate attached hardware

- VHDL simulation: cycle accurate a timing model

- Typically: Simulation of logical behaviour

- Somewhat precise waveform output

### Virtualize the hardware

▲ロ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ● ○ ○ ○

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

- VHDL simulation: cycle accurate a timing model

- Typically: Simulation of logical behaviour

- Somewhat precise waveform output

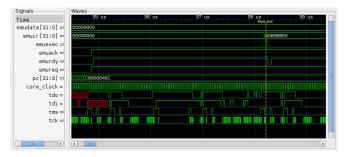

#### Figure: Timing accurate simulation

#### Make ants meet

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

#### Make antz meet...

Drawing by Britta Schneider

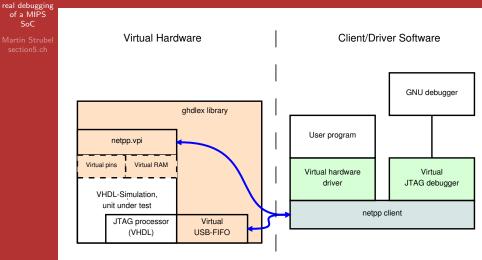

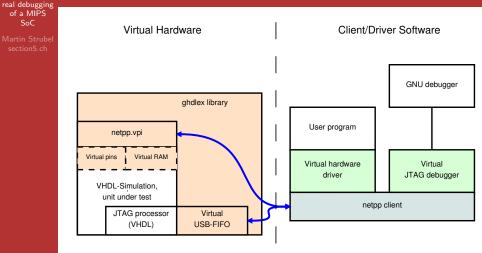

# Now seriously: make ends meet

Distributed, virtual and real debugging of a MIPS SoC

#### Martin Strubel section5.ch

#### Task: Make real world software speak to virtual hardware.

# Result: **ghdlex** *OpenSource* simulator extension library:

- Describe virtual board in  $XML \longrightarrow$

- Attach virtual components in HDL design:

- JTAG debugger

- shared RAM

- USB FIFO

- I/O pins, registers

| 🗢 device                                     | GHDLSimInterface ♂ ↔ \$ +> ↔ x +  |  |  |  |

|----------------------------------------------|-----------------------------------|--|--|--|

| id                                           | ghdlsim                           |  |  |  |

| name                                         | GHDLSimInterface                  |  |  |  |

| protocol                                     | ○ REGISTER ● PROPERTY ○ COMMAND   |  |  |  |

| ▶ revision ♂ ↔ \$ +> ↑ ×                     |                                   |  |  |  |

| A (virtual) register map:                    |                                   |  |  |  |

| ▶ registermap FPGA_Registers ♂ ↔ \$ +> → X + |                                   |  |  |  |

| 🗕 group                                      | ) VirtualPins ♂⇔\$ + ↔ <b>× +</b> |  |  |  |

| name VirtualPins                             |                                   |  |  |  |

| ▶ property Enable ♂ ↔ \$ +> ↑ X +            |                                   |  |  |  |

| ▶ property Reset ♂ ↔ \$ +> ○ X +             |                                   |  |  |  |

| ▶ property Timeout ♂ ↔ \$ ↔ <b>&gt; X +</b>  |                                   |  |  |  |

| ▶ property Throttle ♂ ↔ \$ → > X +           |                                   |  |  |  |

| ▶ property Irq → ↔ ⇒ → → × +                 |                                   |  |  |  |

| group VirtualJTAG                            |                                   |  |  |  |

| name VirtualJTAG                             |                                   |  |  |  |

| ▶ struct Fifo ♂ ↔ \$ +> > <b>x</b> +         |                                   |  |  |  |

Figure: XML hardware description

# Virtual Hardware

Distributed.

virtual and

# Virtual Hardware

Expose design components to the network!

Distributed.

virtual and

SoC

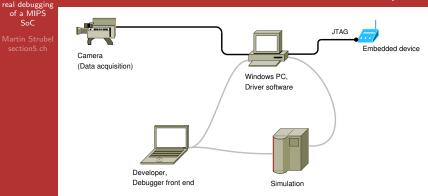

# Distributed processing

Distributed.

virtual and

of a MIPS SoC

> **ghdlex** speaks **netpp** (network property protocol), therefore things can run anywhere.

- HDL-Simulation on powerful main frame

- Data routing from real world software on Windows PC to simulation

- Debugger (Laptop) connecting to any of the debug servers

# Now, where's the bug?

▲ロト ▲周ト ▲ヨト ▲ヨト 三日 - のくぐ

Distributed, virtual and real debugging of a MIPS SoC

- Bug could sit:

- .. in peripheral access (HDL design), or the CPU

- .. in SoC firmware (Code running on CPU core)

- .. in host (PC) software

# Now, where's the bug?

▲ロ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ▶ ● ○ ○ ○

Distributed, virtual and real debugging of a MIPS SoC

- Bug could sit:

- .. in peripheral access (HDL design), or the CPU

- .. in SoC firmware (Code running on CPU core)

- .. in host (PC) software

- .. in Debugger components itself (reserve many gaelic curses)

- .. between two human ears

# Now, where's the bug?

Distributed, virtual and real debugging of a MIPS SoC

- Bug could sit:

- .. in peripheral access (HDL design), or the CPU

- .. in SoC firmware (Code running on CPU core)

- .. in host (PC) software

- .. in Debugger components itself (reserve many gaelic curses)

- .. between two human ears

- Avoid to introduce bugs during development:

- Verify CPU behaviour against **qemu** (functional simulation)

- Keep device configuration in exactly one XML file

- Use Makefile rules or similar to keep source and generated files in sync ( $\rightarrow$  GNU make)

- Introduce detection mechanisms: ID codes or functionality descriptors (JTAG USERCODE register)

\*ロ \* \* ● \* \* ● \* \* ● \* ● \* ● \* ●

Martin Strube section5.ch

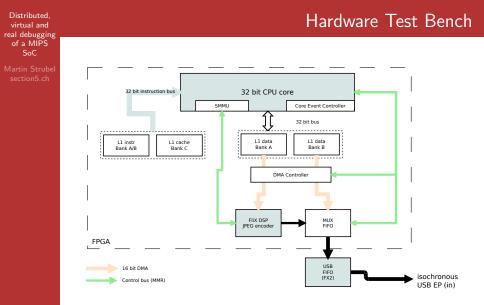

Demos:

- 1 Debugging the simulation

- 2 Debugging the hardware: HDR-60 FPGA camera kit

- 8 Verifying the CPU using qemu

Figure: JPEG encoder test bench

\*ロ \* \* ◎ \* \* ● \* \* ● \* ● \* \* ● \* \* ● \* \* ● \* \* ● \* \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● ● \* ● ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● \* ● ● \* ● ● \* ● ● \* ● ● \* ● ● ● \* ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ●

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○ ○○○

Distributed, virtual and real debugging of a MIPS SoC

Martin Strubel section5.ch

- Questions?

- More about device hardware XML description:

- $\rightarrow \, \mathsf{http://www.section5.ch/netpp}$

- Don't miss René's Introduction to his Mais MIPS core (later today in this session)

#### Thank you for listening!

www.section5.ch

The interface between the JTAG port and the CPU: a somewhat generic HDL library.

- Vendor independent interface ('standard' register set)

- Supports Xilinx and Lattice native JTAG components

- CPU core architecture independent

- Software support by emulation library (Python, uniproxy debug server)

(日) (日) (日) (日) (日) (日) (日) (日) (日)

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 三臣 - のへぐ

Martin Strubel section5.ch

| Register | Description              | Signals               |

|----------|--------------------------|-----------------------|

| EMUSTAT  | ICE and CPU state        | emuack, emurdy, state |

| EMUCTRL  | ICE control              | emurequest, (emuexec) |

| EMUIR    | ICE instruction register | 32 bit (to core)      |

| EMUDATA  | ICE data register        | 32 bit (from core)    |

#### Table: TAP registers

Actual register addressing is TAP (FPGA family) specific