Continuous integration (‘CI’) for hardware is a logical step to take: Why not do for hardware, what works fine for software?

To keep things short: I’ve decided to stick my proprietary RISC-V approach ‘pyrv32’ into the opensourced MaSoCist testing loop to always have an online reference that can run anywhere without massive software installation dances.

Because there’s still quite a part of the toolchain missing from the OpenSource repo (work in progress), only a stripped down VHDL edition of the pyrv32 is available for testing and playing around.

This is what it currently does, when running ‘make all test’ in the provided Docker environment:

- Build some tools necessary to build the virtual hardware

- Compile source code, create a ROM file from it as VHDL

- Build a virtual System on Chip based on the pyrv32 core

- Downloads the ‘official’ riscv-tests suite onto the virtual target and runs the tests

- Optionally, you can also talk to the system via a virtual (UART) console

Instructions

This is the quickest ‘online’ way without installing software. You might need to register yourself a docker account beforehand.

- Log in at the docker playground: https://labs.play-with-docker.com

- Add a new instance of a virtual machine via the left panel

- Run the docker container:

docker run -it hackfin/masocist - Run the test suite:

wget section5.ch/downloads/masocist_sfx.sh && sh masocist_sfx.sh && make all test - Likewise, you can run the virtual console demo:

make clean run-pyrv32 - Wait for Boot message and # prompt to appear, then type h for help.

- Dump virtual SPI flash:

s 0 1 - Exit minicom terminal by Ctrl-A, then q.

What’s in the box?

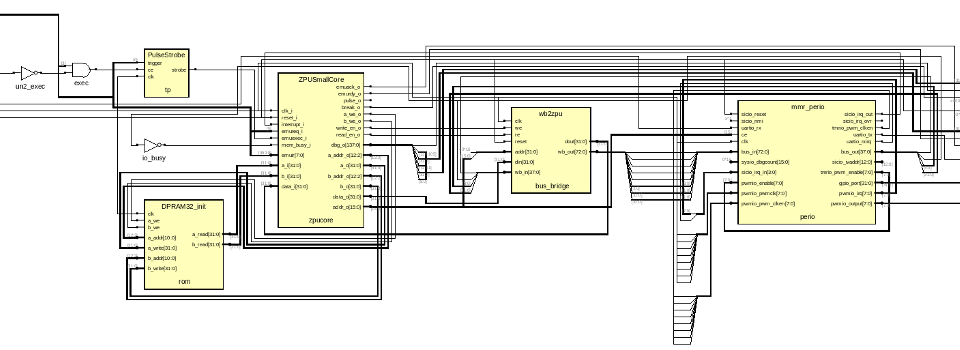

- ghdl, ghdlex: Turns a set of VHDL sources into a simulation executable that exposes signals to the network (The engine for the virtual chip).

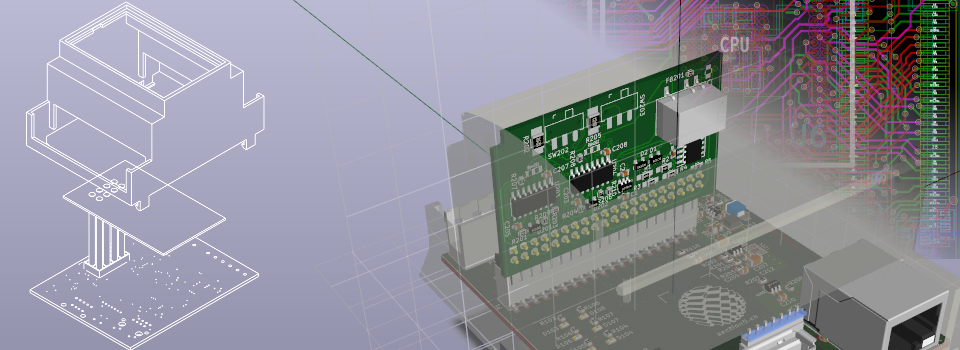

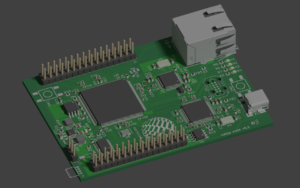

- masocist: A build system for a System on Chip:

- GNU Make, Linux kconfig

- Plenty of XML hardware definitions based on netpp.

- IP core library and plenty of ugly preprocessor hacks

- Cross compiler packages for ZPU, riscv32 and msp430 architectures

- gensoc: SoC generator alias IP-XACT’s mean little brother (from another mother…)

- In-House CPU cores with In Circuit Emulation features (Debug TAPs over JTAG, etc.):

- ZPUng: pipelined ZPU architecture with optimum code density

- pyrv32: a rv32ui compatible RISC-V core

- Third party opensource cores, not fully verified (but running a simple I/O test):