Overview:

- MaSoCist SoC builder

- Cottonpicken Engine

- Image compression / JPEG Encoder IP

- cCAP: customizeable application processors and System on Chip solutions for networking and video processing

The MaSoCist build system

Pun intended: Applying a linux kernel configuration approach onto a hardware system turned out to be painful. However, it pays off:

- Cross platform: Simulate and synthesize reusable code for various architectures (Lattice, Xilinx, Altera FPGAs)

- Configure peripheral interface instances like a linux kernel

- Automated generation of address decoders, peripheral instances and memory map from gensoc – our in house SoC generator.

- Generate hardware configuration, software drivers and corresponding register documentation in one call: ‘make all’

- Continuous integration for hardware designs: Run test benches automatically in the cloud for hardware verification

It allows vendor specific designs and extensions without the need to OpenSource, therefore it is available in two license variants:

- Limited OpenSource, now hosted at github: https://github.com/hackfin/MaSoCist

- Full SDK/HDK under Custom Vendor license

A fully usable Docker container is hosted at: https://hub.docker.com/r/hackfin/masocist/, use

docker pull hackfin/masocist

to download this container. If you want to run this on a Windows client, see Windows setup notes.

MaSoCist opensource primer: [sdm_download id=”1412″ fancy=”0″]

IP blocks and cores

Cottonpicken Engine

The Cottonpicken Engine is an in-house micro coded digital signal processing (DSP) engine that has the following functionality:

- Bayer pattern decoding into various formats (YUV 4:2:2, YUV 4:2:0, RGB, programmable delays)

- YUV conversion supports YCrCb, YCoCg as well

- 3×3, 5×5 filter kernels

- Specific matrix operations, cascadeable

It is capable of running at full data clock (pixel clock) up to 150 MHz (platform dependent).

The engine is only available as a closed source netlist object as part of a development package.

Image compression

JPEG Encoder IP

Our in-house designed, machine vision proof JPEG encoder and streaming solutions available for usage in standard FPGAs at low costs (at typically below 35’000 EUR support costs per project). The supported pixel bit depth is up to 12 bits. The JPEG IP is available in two standalone variants:

- L1 monochrome multiplexed pipeline (150 MHz pixel clock on Spartan6)

- L2 dual pipe simultaneous encoding for high quality YUV422, for example 1280×720@60fps (up to 100 MHz pixel clock)

- L2H: Higher pixel clock variant (up to 200MHz) available for specific platforms

Fully deployable UDP/Ethernet (RFC 2435) streaming solutions and camera reference designs are available as well. The receiver’s software side is covered with embedded gstreamer OpenSource appplications that run on Linux and Windows platforms, likewise.

[ more … ]

Lossless and other compression methods

We have extensive know how on:

- High speed DPCM-Compression (up to 200 MHz pixel clock, 16 bit, lossless, suitable for medical images, full simulation model available). Can be made software-compatible to lossless JPEG (not JPEG-LS).

- Multirate adaptive predictors for special imagery (lossy coding / quantization support)

- Wavelet coding kernels (lossy and lossless)

- Combined, lossy approaches, non-standard (partial JPEG2000 transcoding possible)

- Huffman/Golomb-Rice coding IP core, dual-channel (simultaneous throughput of Luma/Chroma channels).

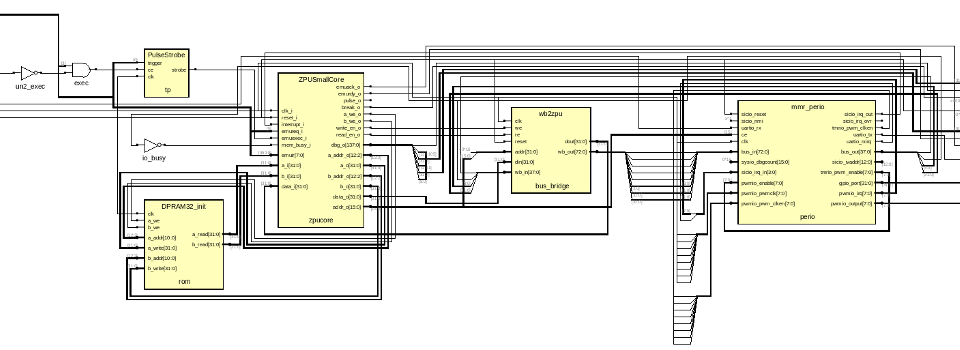

cCAP SoC Reference designs

These System on Chip designs consist of a fully configureable CPU plus standard peripherals and can be customized with special interfaces. The CPU can be programmed with GCC and is accessed via ICE JTAG during development. The underlying build and configuration system and some of the peripherals are available as Open Source, see MaSoCist.

[ more … ]

Simulation models

Full simulation models are available for all our IP cores that can be co-simulated with custom IP or run ‘live’:

See also VirtualChip page.